| FEXT’97pllをcpldのクロック源としてつかう | ||||||||||||||||||||||||

|

1998/9/7(98/09/08) |

||||||||||||||||||||||||

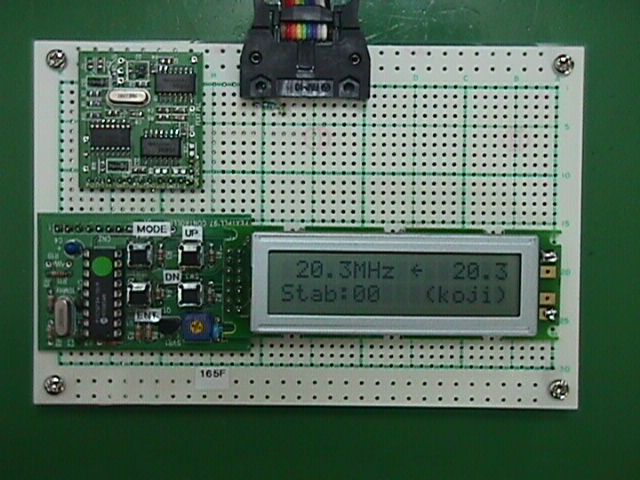

| NiftyserveのFEXT(エキステンダーフォーラム)で、(こじ)さんが中心になって開発された、FEXT'97PLLキットをCPLD実験回路のクロック源としてつかってみました。 クロックを100KHzきざみでスムーズに変更できるので非常に便利です。 今さらという感じではあります。(もっと早く使えば良かったという意味) 市販のユニバーサル基板の上に乗せました。 使ったのは初期型のキットなのですが、いまのタイプは高いほうがもっとでるようになっているはずです。 |

||||||||||||||||||||||||

|

|

||||||||||||||||||||||||

|

|

||||||||||||||||||||||||

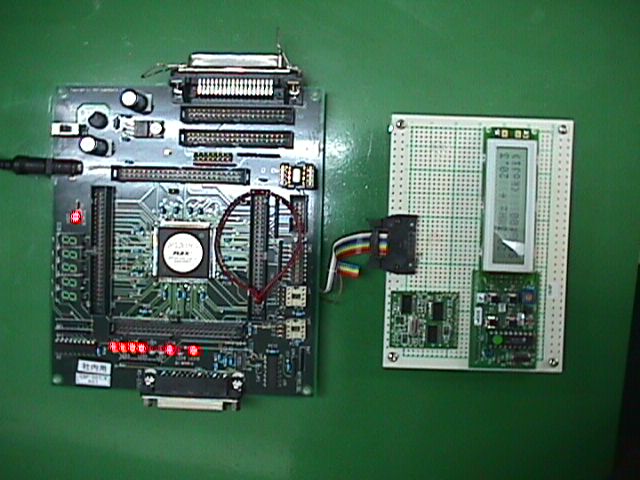

| このように弊社ブレッドボードのクロック源としてつかっています。 | ||||||||||||||||||||||||

|

|

||||||||||||||||||||||||

|

Copyright(c) 1998 a-ushiro / HuMANDATA LTD. |

||||||||||||||||||||||||

|

|

||||||||||||||||||||||||

|

|

||||||||||||||||||||||||