丂惗夋憸偲壛岺夋憸傪LCD偵摨帪偵昞帵傑偡丅暘妱埵抲偼僞僢僠偵傛傝曄峏壜擻偱偡丅

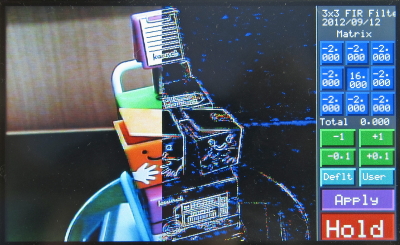

丒摦夋昞帵帪丗幚嵺偺塮憸亄僴乕僪僂僃傾偵傛傞忯傒崬傒塮憸

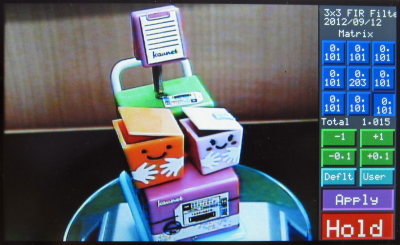

丒儂乕儖僪帪丗幚嵺偺塮憸亄僜僼僩僂僃傾偵傛傞忯傒崬傒塮憸

埲慜偺幚尡儁乕僕偼壓婰傪偛棗偔偩偝偄丅

丒ALTERA FPGA偵捈愙庢崬傒LCD偵昞帵

丒ALTERA FPGA偵捈愙庢崬傒丄夋憸張棟傪偐偗偰LCD偵昞帵

仧婡婍峔惉

僋儕僢僋偟偰奼戝 |

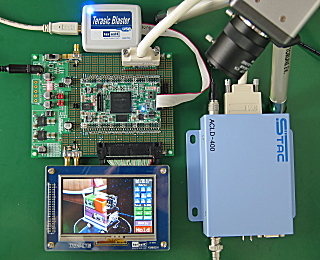

巊梡婡婍 | ||

| 婡婍柤 | 宆斣 | 儊乕僇 | |

|---|---|---|---|

| Cyclone IV GX FPGA儃乕僪 (僩儔儞僔乕僶枹巊梡) |

ACM-024 | 僸儏乕儅儞僨乕僞 | |

| 揹尮晅偒儐僯僶乕僒儖婎斅 | ZKB-105 | 僸儏乕儅儞僨乕僞 | |

| 傾僫儘僌 僇儊儔儕儞僋 僪儔僀僶乕 | ACLD-400 | 姅幃夛幮僗僞僢僋條 | |

| 4.3僀儞僠 LCD 僞僢僠僷僱儖 | TRDB-LTM(僨傿僗僐儞昳) | Terasic 屳姺昳偲偟偰UTL-021傪斕攧偟偰偍傝傑偡  5"僞僢僠僷僱儖晅偒TFT-LCD 5"僞僢僠僷僱儖晅偒TFT-LCD |

|

| 僇儔乕CCD僇儊儔 | TR-1300C | 僐儘僫揹嬈乮姅乯條 | |

| 僟僂儞儘乕僪働乕僽儖 | Terasic Blaster | Terasic幮 | |

仧忯傒崬傒乮僐儞儃儕儏乕僔儑儞乯

丂昞帵偡傞夋慺僨乕僞傪丄帺恎偺廃曈夋慺僨乕僞傪尦偵曄壔偝偣傞庤朄偱偡丅崱夞偼丄FPGA偺僽儘僢僋儊儌儕忋偵拁偊傜傟偨僨乕僞傪丄揔愗側僞僀儈儞僌偱撉傒弌偡偙偲偱丄3x3僐儞儃儕儏乕僔儑儞傪峴偭偰偄傑偡丅

| (x-1,y-1) | (x,y-1) | (x+1,y-1) |

| (x-1,y) | (x,y) | (x+1,y) |

| (x-1,y+1) | (x,y+1) | (x+1,y+1) |

張棟拞偺嵗昗傪(x,y)偲偡傞偲丄(x-1,y-1)偐傜(x+1,y+1)偺9僺僋僙儖偑昁梫偲側傝傑偡丅

| (x-2,y-2) | (x-1,y-2) | (x,y-2) |

| (x-2,y-1) | (x-1,y-1) | (x,y-1) |

| (x-2,y) | (x-1,y) | (x,y) |

崱夞偼1峴亄1僺僋僙儖抶傜偣傞偙偲偱丄(x-2,y-2)偐傜(x,y)傑偱偺9僺僋僙儖傪巊梡偟丄(x-1,y-1)偺夋慺傪弌椡偟偰偄傑偡丅

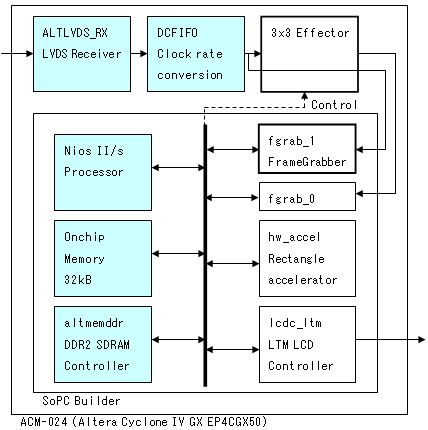

仧僔僗僥儉峔惉

丂FPGA撪晹峔惉偼埲壓偺傛偆偵側偭偰偄傑偡丅 "3x3 Effector"偵傛傝丄儕傾儖僞僀儉偵忯傒崬傒張棟傪峴偄傑偡丅僼儗乕儉僌儔僶乕偑俀偮搵嵹偝傟丄壛岺慜丄壛岺屻偺俀庬椶偺僨乕僞傪庢摼壜擻偵偟偰偄傑偡丅俀庬椶偺夋憸僨乕僞偼LCD偺嵍塃偵暘偗偰昞帵偝傟傑偡丅

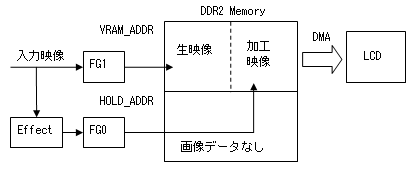

仧撪晹張棟丗儕傾儖僞僀儉昤夋帪

丂擖椡偝傟偨塮憸僨乕僞偼丄柍壛岺偱FG1偵傛傝RAM乮LCD昞帵偺嵍懁乯偵奿擺偝傟傑偡丅

僄僼僃僋僞偵傛傝壛岺傪峴偭偨僨乕僞偼丄FG0偵傛傝RAM乮LCD昞帵偺塃懁)偵奿擺偝傟傑偡丅

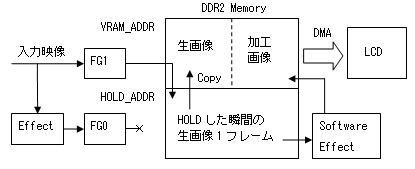

仧撪晹張棟丗HOLD帪

丂HOLD帪偼僜僼僩僂僃傾偱夋憸張棟傪峴偭偰偄傑偡丅

傑偢HOLD偟偨弖娫偺夋憸僨乕僞傪丄RAM偺昤夋僄儕傾奜偵曐娗偟傑偡丅偙偺僨乕僞傪僜僼僩僂僃傾偱壛岺偟丄RAM偺昤夋僄儕傾塃懁偵奿擺偟偰偄傑偡丅

仧幚嵺偺夋憸

丂幚嵺偵僄僼僃僋僩傪妡偗偨夋憸傪丄LCD偵昞帵偟偨帪偺夋憸傪帵偟傑偡LCD夋柺拞墰埵抲傛傝塃懁偑僄僼僃僋僩偺偐偐偭偨夋憸偵側傝傑偡丅

丒椫妔拪弌乮僉儍儔僋僞乯

僋儕僢僋偟偰奼戝

丒暯妸壔乮僉儍儔僋僞乯

僋儕僢僋偟偰奼戝

丒椫妔拪弌乮僥僉僗僩乯

僋儕僢僋偟偰奼戝

丒暯妸壔乮僥僉僗僩乯

僋儕僢僋偟偰奼戝

仧夞楬僨乕僞偵偮偄偰

丂摉幮偱偼丄捠忢丄僒儞僾儖夞楬側偳偺偛採嫙偼峴偭偰偍傝傑偣傫丅娫堘偄側偳尒偮偗傜傟傑偟偨傜偤傂偛巜揈壓偝偄丅